DAQ system: Difference between revisions

No edit summary |

|||

| Line 72: | Line 72: | ||

When [[Gammasphere]] collects data, single-ended [[Detector Signals|signals]] are first collected from the slope box for the Ge Center, Ge Sides, and BGO segment. The signals are converted to differential signals by the [[The Slope Box Extension|SBX]], and are then sent to the collector box so the signals can properly be routed to the digitizers. The digitizers process and output the desired information to the user based upon their data specifications. The DAQ system is an FPGA-based design that provides communication hub interfacing the [[Preamplifier|preamp]], power board, dongle and slope box to EPICS through serial interface. Analog signal paths are completely software controlled. | When [[Gammasphere]] collects data, single-ended [[Detector Signals|signals]] are first collected from the slope box for the Ge Center, Ge Sides, and BGO segment. The signals are converted to differential signals by the [[The Slope Box Extension|SBX]], and are then sent to the collector box so the signals can properly be routed to the digitizers. The digitizers process and output the desired information to the user based upon their data specifications. The DAQ system is an FPGA-based design that provides communication hub interfacing the [[Preamplifier|preamp]], power board, dongle and slope box to EPICS through serial interface. Analog signal paths are completely software controlled. | ||

==DAQ System Function== | ==DAQ System Function== | ||

The DAQ system prior to upgrades consisted of VME crates, IOC Modules, Digitizers and Trigger Modules. There were two types of Digitizers (Master and Slave) and well as Trigger (Master and Router) | The DAQ system prior to upgrades consisted of VME crates, IOC Modules, Digitizers and Trigger Modules. There were two types of Digitizers (Master and Slave) and well as Trigger (Master and Router). All channels in all digitizers run continuously. When discriminator logic marks leading edges of gamma-ray signals, energy sums, timing and other data are stored in a header identifying the event. If the event is selected for readout by the trigger system, the header and a programmable amount of waveform is transferred from the channel to the board-wide FIFO (first in, first out) data holder. The IOC scans the FIFOs to see if there is data to read out. If so, the IOC reads it out into buffers. A program called “gtReceiver” sends messages to each IOC when the receiver is ready for more data. The IOC then breaks apart buffers into UDP packets and sends them to gtReceiver. The gtReceiver program then routes the packets to files that may be organized by digitizer or by channel. | ||

<imagemap> | <imagemap> | ||

Image:DAQSystem.png|center|thumb|700px|Figure 2. Diagram of the DAQ system process. | Image:DAQSystem.png|center|thumb|700px|Figure 2. Diagram of the DAQ system process. | ||

Revision as of 01:13, March 30, 2023

This is an image map. Click on a section of the picture to go to the page for that item.

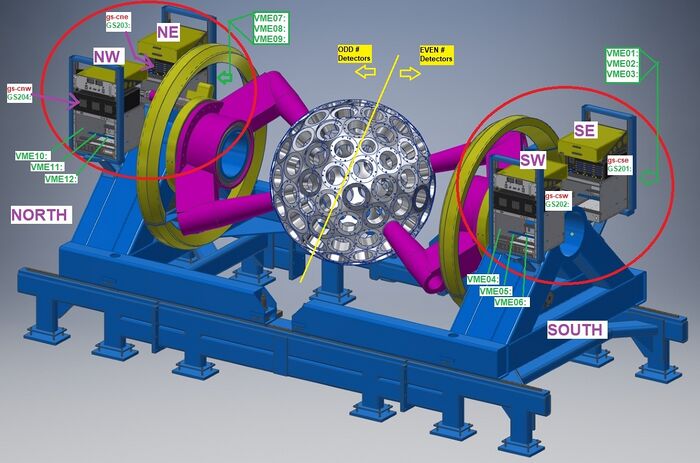

Gammasphere's DAQ system (data acquisition system) is now placed on relay racks by each side of its "hemispheres". Each of the racks for the DAQ consists of a power supply, a collector box, and a VME crate. The data acquisition system observes, interprets, and modifies data taken from Gammasphere and appropriately presents it to the user.

The picture above provides an overall map to the naming conventions associated with the system. Cardinal directions are shown in purple text, process variable (EPICS) names are shown in green text and network IDs are shown in red text. There are multiple computers within the DAQ system:

ln2con || 192.168.203.148 || Linux computer that lnfill boots from| Network name | IP address | Description |

|---|---|---|

| ioc01: | 192.168.203.141 | MVME5500 VME processor used for control and readout |

| ioc02: | 192.168.203.142 | MVME5500 VME processor used for control and readout |

| ioc03: | 192.168.203.143 | MVME5500 VME processor used for control and readout |

| ioc04: | 192.168.203.144 | MVME5500 VME processor used for control and readout |

| ioc05: | 192.168.203.145 | MVME5500 VME processor used for control and readout |

| ioc06: | 192.168.203.177 | MVME5500 VME processor used for control and readout |

| ioc07: | 192.168.203.178 | MVME5500 VME processor used for control and readout |

| ioc08: | 192.168.203.179 | MVME5500 VME processor used for control and readout |

| ioc09: | 192.168.203.180 | MVME5500 VME processor used for control and readout |

| ioc10: | 192.168.203.183 | MVME5500 VME processor used for control and readout |

| ioc11: | 192.168.203.181 | MVME5500 VME processor used for control and readout |

| ioc12: | 192.168.203.182 | MVME5500 VME processor used for control and readout |

| gs-cne | 192.168.203.88 | Raspberry Pi inside the North East Collector box |

| gs-cnw | 192.168.203.149 | Raspberry Pi inside the North West Collector box |

| gs-cse | 192.168.203.42 | Raspberry Pi inside the South East Collector box |

| gs-csw | 192.168.203.26 | Raspberry Pi inside the South West Collector box |

| gs-pdu-north | 192.168.203.224 | Power Distribution Unit for the North Hemisphere |

| gs-pdu_south | 192.168.203.225 | Power Distribution Unit for the North Hemisphere |

| gs-ts-north | 192.168.203.91 | Terminal server providing console port access for ioc07 through ioc12 |

| gs-ts_south | 192.168.203.186 | Terminal server providing console port access for ioc01 through ioc06 |

| lnfill | 192.168.203.121 | Embedded VME processor that hosts the EPICS databases for valve status and valve control |

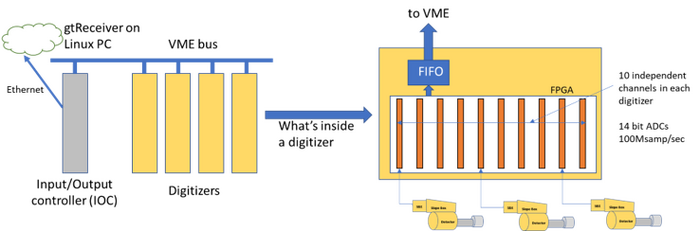

When Gammasphere collects data, single-ended signals are first collected from the slope box for the Ge Center, Ge Sides, and BGO segment. The signals are converted to differential signals by the SBX, and are then sent to the collector box so the signals can properly be routed to the digitizers. The digitizers process and output the desired information to the user based upon their data specifications. The DAQ system is an FPGA-based design that provides communication hub interfacing the preamp, power board, dongle and slope box to EPICS through serial interface. Analog signal paths are completely software controlled.

DAQ System Function

The DAQ system prior to upgrades consisted of VME crates, IOC Modules, Digitizers and Trigger Modules. There were two types of Digitizers (Master and Slave) and well as Trigger (Master and Router). All channels in all digitizers run continuously. When discriminator logic marks leading edges of gamma-ray signals, energy sums, timing and other data are stored in a header identifying the event. If the event is selected for readout by the trigger system, the header and a programmable amount of waveform is transferred from the channel to the board-wide FIFO (first in, first out) data holder. The IOC scans the FIFOs to see if there is data to read out. If so, the IOC reads it out into buffers. A program called “gtReceiver” sends messages to each IOC when the receiver is ready for more data. The IOC then breaks apart buffers into UDP packets and sends them to gtReceiver. The gtReceiver program then routes the packets to files that may be organized by digitizer or by channel.

To view how this system is controlled, go to DGS Commander EDM Screens.

Go back to Digital Gammasphere Upgrade Project