ANL Digitizer Firmware for Advanced Users: Difference between revisions

No edit summary |

|||

| Line 1: | Line 1: | ||

== A Short Introduction to Hardware == | == [[A Short Introduction to Data Acquisition Hardware]] == | ||

To fully understand how the firmware works the hardware environment must be explained. | To fully understand how the firmware works the hardware environment must be explained. This section briefly introduces the concept of '''Master and Slave digitizers''', '''Clocking and Timestamps''', and '''Connecting the Trigger to External Systems'''. | ||

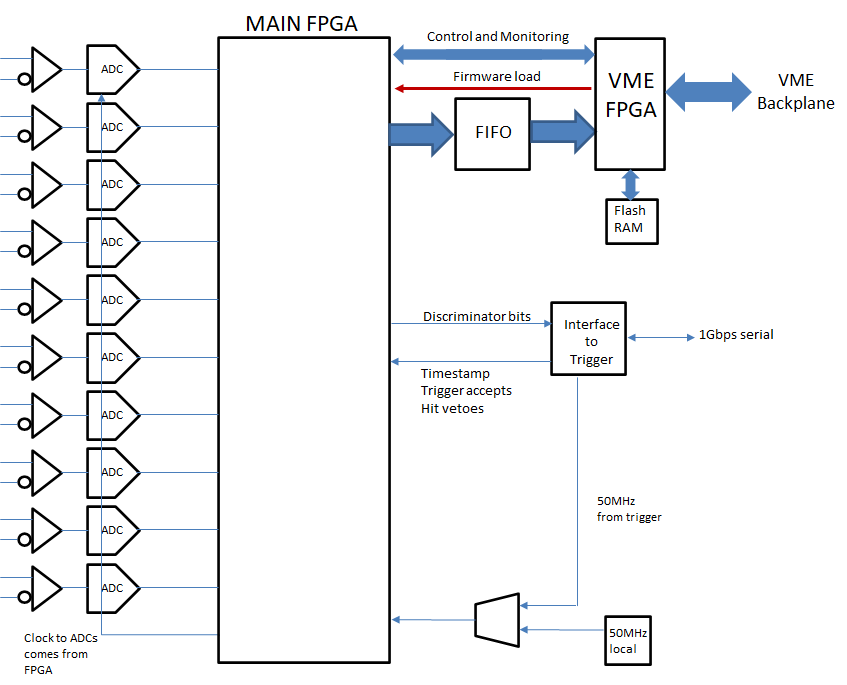

The digitizer module contains two FPGAs, one for VME interface and firmware maintenance purposes, and the other for ADC data processing, as shown in Figure 1. | The digitizer module contains two FPGAs, one for VME interface and firmware maintenance purposes, and the other for ADC data processing, as shown in Figure 1. | ||

Revision as of 15:57, September 29, 2021

A Short Introduction to Data Acquisition Hardware

To fully understand how the firmware works the hardware environment must be explained. This section briefly introduces the concept of Master and Slave digitizers, Clocking and Timestamps, and Connecting the Trigger to External Systems.

The digitizer module contains two FPGAs, one for VME interface and firmware maintenance purposes, and the other for ADC data processing, as shown in Figure 1.

Input Signals

Signals at the digitizer input are differential. The input range is limited. While the ADC chip the module uses nominally has a +/-2V differential input (that is, + to – may range from -2V to +2V) the input buffer circuitry does not have sufficient power supply voltage headroom to support this full range. The device works very well for signals that range between -1.5V to +1.5V differential, but signal compression occurs beyond those limits. Linearity studies performed at ANL show that the device is almost perfectly linear for an input range of -1.2V to +1.2V but small deviations from linearity are discernable from 1.2V to 1.5V with marked deviations occurring past 1.5V.

In terms of ADC counts, since the ADC chip is designed to span 16,384 codes over 4 volts, this means that the conversion is 4096 counts per volt. Thus

- For absolute best linearity, limit the DC offset and signal range to no more than ±(1.2 * 4096), or ±4916 counts, from the nominal 0V level of 8192 counts (3276 to 13108).

- For all but the most stringent requirements, a more relaxed range of ±(1.5 * 4096), or ±6144 counts, will suffice (2048 to 14336).

- If the physical setup exceeds these bounds, non-linearity will distort waveform shapes.

"Master" and "Slave" Digitizers

The digitizer modules may be used in pairs where one digitizer is labeled the “master” and the other is labeled the “slave”. In this configuration the two digitizers have different versions of firmware. The “master” digitizer alone connects to the trigger system. A ribbon cable connects the “master” digitizer to the “slave” digitizer. The “slave” digitizer channels are normally configured to use signals from the “master” digitizer as part of the logic determining if discriminators within the “slave” channels will fire or not, or whether events within the “slave” are marked for readout or not.

Clocking and Timestamps

The ADC chips run at a frequency of 100MHz (100 MSamp/sec). The device may run from its own internal oscillator or may receive a clock from an external trigger system and synchronize to that clock. A clock distribution from the trigger allows many digitizer modules to run synchronous to each other.

The digitizer module uses a 48-bit timestamp counter run from the 100MHz clock. When connected to the trigger system, the trigger may issue a command to synchronously reset the timestamp in all digitizers. Events read out of the digitizer are tagged with a timestamp for sorting and analysis.

Connection to External Trigger System

Digitizer modules may connect to a trigger system for synchronization and event selection purposes. A separate cable plant connects digitizer modules to trigger modules; on the digitizer end the cable uses the same RJ45 connector as Ethernet, but the signal levels and usage are not Ethernet. Do not connect the digitizer to an Ethernet port, this will damage the digitizer module.

The digitizer can run standalone without being connected to a trigger system. In this configuration every digitizer board has independent and unsynchronized clocks. Timestamps for event sorting are not useful across multiple modules as there is no synchronism, but within one board timestamps are still sensible.

See MyRIAD_USER_Manaual or MyRIAD_Abridged_User_Notes in Original Content prior to the ''Gammasphere Upgrade Project'' for detailed information on External Trigger systems.

General Design of the Firmware

The ANL version of digitizer firmware implements ten independent data acquisition pipelines in ten channels. Pileup detection & rejection is performed locally within the digitizer. Selective readout of events is achieved using an external trigger system. Waveform readout of all events is possible, with up to 1024 ADC samples per channel per event, although this will limit the event rate as the VME backplane reaches its bandwidth limit. A down-sampling mode allows readout of averaged samples where each waveform sample in the readout may be the average of 2n ADC samples, from 2 to 128 (n = 0, 1, 2,…, 6, 7). Increased event rates are obtained by limiting the amount of waveform data read out per event.

Each channel pipeline consists of a series of memory buffers used for delay. Discriminator logic recognizes edges within the input signal and causes data values to be sampled. When sampling occurs, the timestamp value is saved. The discriminator logic may be configured as either leading-edge (slope) or constant-fraction architecture, sensitive to either positive-only, negative-only or both edges. The discriminator implements a programmable hold-off time to ensure that the discriminator fires only once per edge. A discriminator firing captures timing and data sums simultaneously. This data is buffered so that discriminator re-arms very quickly. Firing rates over 1MHz can be supported, yet readout is limited to the IOCs total bandwidth (IOC Code Design). No information reduction occurs in pileup conditions due to the fast discriminator recovery time.

All sampled values and sums are formatted into an event header that is followed by a programmable number of waveform samples. The header contains various fields, including the timestamp of the event, the timestamp of the last time the discriminator of that channel fired, the timestamp of the peak, energy information, plus some energy/time information carried over from the previous discriminator firing. Flag bits provide useful diagnostics. The waveform data contains the raw ADC samples of the event, plus serialized timing mark bits that indicate when specific actions (discriminator, peak, timeouts, etc.) occurred and a 2nd bit that indicates whether samples are down-sampled (rescaled average of 2**n samples) or full-speed.

Energy measurement is performed in a double-correlated method timed relative to the moment the discriminator fires. Programmable delay buffers positioned to measure ranges of time before (pre-rise) and after (post-rise) the discriminator logic have accumulators continuously calculating the sum of all the ADC samples within them. When the discriminator fires these sums are saved and reported in the header. These sums may then be used by open source user-maintained software (see the gitlab link in analysis codes for GEBSort) to calculate the energy (amplitude) of the input signal, with all necessary baseline and pole-zero correction information obtained from the other information in the header. This method is arithmetically identical to the traditional “trapezoid” method but is optimized for high rates of discriminator operation.

Hits captured by the discriminator may optionally be rejected if pileup occurs. If piled-up events are allowed the piling-on events may be read out in a variety of ways including extended and offset waveforms or just additional headers. The reverse logic is also supported, in which only piled-up events are available for readout. The firmware interfaces with an FPGA-based trigger system, also designed at ANL, to provide event selection based upon programmable trigger conditions. Specific triggering modes appropriate to the different detector systems at ANL have been developed.

Event Data Nomenclature

Signal edges marked by discriminator firings are named discriminator hits.

- Discriminator hits become accepted hits after passing through pileup rejection logic.

- The firmware may run by itself (“internal accept all” mode) or with the trigger system (“TTCL mode”).

- When running in “internal” mode accepted hits immediately become accepted events that are later read out.

- When the trigger system is used accepted hits wait in a queue for a limited time. The accepted hits in this queue only become accepted events if selected by a trigger accept message from the trigger. Accepted hits not marked as accepted events fall off the end of the pipeline and are discarded.

- The expectation is that all Accepted Events will be read out. Accepted Events that were unable to be copied into the output buffer due to FIFO backup or other readout interference are named dropped events.

- When using the trigger system, the digitizer may assert a Throttle Request to the trigger if its FIFO is getting too full. This request, if honored, will result in the trigger suspending the issuance of trigger accept messages so that the readout system may drain the FIFO forming an automatic flow control mechanism to avoid dropped events.

Discriminator Modes

The firmware supports either leading-edge or constant-fraction discriminator logic, independently selected per channel. In leading-edge mode the operation is controlled by a delay value ‘d’ and a threshold such that the discriminator fires if the difference between sample X(n) and sample X(n-d), after some filtering, is greater than the threshold. In constant-fraction mode, the user specifies a fraction value along with the same timing parameter ‘d’; the discriminator logic continuously calculates [X(n)*fraction] – X(d), and fires when this signal recrosses the initial value it had before the start of the edge.

A 2nd, separate copy of the leading-edge discriminator, with its own threshold, called the coarse discriminator is also provided. The coarse discriminator fires well before the main discriminator does as it sees the edge earlier. The output of this device is used to capture early energy sum values well before the edge occurs, for use in pole-zero and/or baseline correction software after data is collected. Figure 3, later in this document, will explain these terms more fully.

Pileup and Discriminator Hold-Off

When pileup rejection is on, discriminator hits become accepted hits only if there is no pileup.

When pileup rejection is off, discriminator hits always become accepted hits, but differentiation between the first accepted hit and all that pile up upon it (a “pileup train”) is needed

Go back to Digital Gammasphere and the SBX Upgrade