## Digital Gammasphere Firmware User's Manual For experts and firmware nerds only

-- PRELIMINARY --

September 13, 2021 Version 1.0 *This revision of the document describes firmware at SVN revision #6185.*

> Originator: J. Anderson Document #TBA

# Table of Contents

| TABLE OF FIGURES                                                        | 4  |

|-------------------------------------------------------------------------|----|

| INTRODUCTION                                                            | 5  |

| DETAILS OF EACH CHANNEL                                                 | 5  |

| MEMORY STRUCTURES WITHIN XILINX FPGAS                                   | 5  |

| IMPORTANT FPGA GENERALITIES                                             |    |

| CHANNEL INITIALIZATION                                                  |    |

| Best initialization practice                                            | 8  |

| SPECIFICS OF DISCRIMINATOR OPERATION                                    | 9  |

| OPERATION IN THE LEADING-EDGE DISCRIMINATOR MODE                        |    |

| Discriminator Hold-off                                                  |    |

| Preamp Reset Kill                                                       |    |

| Peak Detector                                                           |    |

| DIFFERENCE IN OPERATION OF THE CONSTANT-FRACTION MODE                   |    |

| Time interpolation using the CFD Sample values                          |    |

| Detecting improper CFD operation                                        |    |

| DETAILS OF PILEUP LOGIC                                                 |    |

| HANDLING OF PILEUP                                                      |    |

| Relationship of pileup to event header formation                        |    |

| PEHQ latch timing requirements                                          |    |

| HOLDOFF TIME VERSUS PILEUP TIME                                         | 20 |

| EVENT FORMATION AT THE END OF THE PILEUP INSPECTION TIME                | 21 |

| Triggered modes vs. "Internal Accept All"                               |    |

| Event expiry                                                            |    |

| Event status bits in the PEQ                                            |    |

| EXTERNAL DISCRIMINATOR MODES                                            |    |

| External Discriminator Signals                                          | 24 |

| Timestamp-based external discriminator                                  | 25 |

| INSERTION OF TIMING MARKS INTO THE WAVEFORM                             | 26 |

| TIMING MARKS AND LONG WAVEFORM READOUTS                                 |    |

| TIMING MARKS AND DOWN-SAMPLING                                          | 27 |

| FORMATION OF TIMING MARKS                                               |    |

| ENERGY SUMMATION                                                        |    |

| P2 AND ENERGY SUMS                                                      | 30 |

| MULTIPLE PRE-RISE SUMS                                                  |    |

| DATA READOUT AT THE CHANNEL LEVEL                                       | 31 |

| READOUT GENERAL OPERATION WHEN PILEUP IS REJECTED                       | 31 |

| Readout in "internal accept all" – pileup rejected                      |    |

| Effects of long waveform length settings; defining Readout Interference |    |

| Down-sampled readout                                                    |    |

| READOUT OF PILED-UP EVENTS                                              |    |

| STOP READING HERE                                                       |    |

| STOP READING HERE                                                       |    |

| STOP READING HERE                                                       |    |

| Data Format                                                             | 37 |

| Data Header – leading-edge discriminator mode                           |    |

| Data Header – CFD mode                                                  |    |

|                                                                         |    |

| WAVEFORM DATA FORMAT DETAILS                                          |    |

|-----------------------------------------------------------------------|----|

| ENERGY SUMMATION LOGIC OPERATIONAL DETAILS                            |    |

| Comparison of delays and sums versus the standard trapezoidal filter  |    |

| DISCRIMINATOR FILTER                                                  |    |

| CONSTANT-FRACTION DISCRIMINATOR                                       |    |

| LEADING-EDGE HOLD-OFF INTERACTION WITH CFD OPERATION                  |    |

| TRIGGER DELAY BUFFER                                                  |    |

| Effects of delayed discriminator bit formation                        |    |

| WAVEFORM READOUT GENERALITIES                                         |    |

| DATA COLLECTION ACROSS THE DIGITIZER AND READOUT OVER VME             |    |

|                                                                       |    |

| Waveform Down-Sampling<br>On-Off down-sampling                        |    |

| Pileup and Event Readout                                              |    |

| READOUT INTERFERENCE                                                  |    |

| Readout Interference when Down-sampling is in use                     |    |

| Pileup Extension and Readout Modes                                    |    |

| Readout Modes when Pileup Extension is <u>Disabled</u>                |    |

| Readout operation when Pileup Extension is <u>Enabled</u>             |    |

| · · · · · · · · · · · · · · · · · · ·                                 |    |

| INTERFACE TO THE EXTERNAL TRIGGER                                     | 60 |

| TIMESTAMP SYNCHRONIZATION                                             | 60 |

| EVENT VETO                                                            | 60 |

| TRIGGER DECISION LATENCY                                              | 61 |

| Details of the trigger window calculation                             | 61 |

| OTHER COMMANDS FROM THE TRIGGER                                       | 63 |

| INFORMATION SENT TO THE TRIGGER SYSTEM BY THE DIGITIZER               | 63 |

| DATA FLOW CONTROL (THROTTLE)                                          | 63 |

| SPECIAL TRIGGER MODES                                                 | 64 |

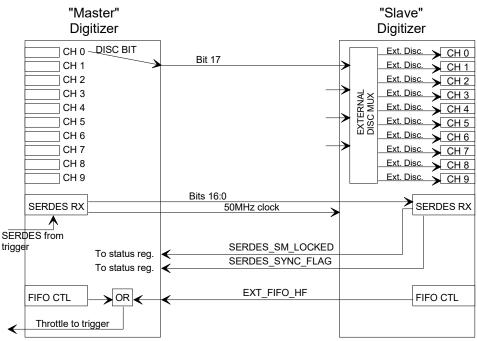

| MASTER AND SLAVE DIGITIZERS                                           | 64 |

| DETAILED DESCRIPTION OF EXTERNAL DISCRIMINATOR MODES                  |    |

| TYPICAL MODES OF SLAVE DIGITIZER OPERATION                            |    |

| Gammasphere "Independent" Mode                                        |    |

| Gammasphere "Clean", "Dirty" and "Module" Modes with Slave Digitizers |    |

| "Pseudo-GRETINA" Mode                                                 |    |

| DIAGNOSTIC CAPABILITIES USING THE ON-BOARD DAC                        |    |

| GLOSSARY                                                              | 71 |

| ULUGGARI                                                              | /1 |

## Table of Figures

| FIGURE 1 - DELAY BUFFERS PER CHANNEL HAVE DIFFERING WIDTHS FOR IMPLEMENTATION OF DELAYS WITHOUT COUNTERS.       | 5     |

|-----------------------------------------------------------------------------------------------------------------|-------|

| FIGURE 2 - TIMING OF CHAIN_INVALID AND SEQUENCED INITIALIZATION THEREAFTER.                                     | 7     |

| FIGURE 3 - USE OF POST-RISE BUFFER TO CREATE DELAYED COPY OF CHAIN_INVALID                                      | 9     |

| FIGURE 4 : PIPELINE FILTER CALCULATION FOR DISCRIMINATOR NOISE REDUCTION                                        |       |

| FIGURE 5 – CHANNEL ARCHITECTURE IN THE LEADING-EDGE DISCRIMINATOR MODE                                          | 10    |

| FIGURE 6 - SIMULATION OF LEADING-EDGE DISCRIMINATOR OPERATION.                                                  | 11    |

| FIGURE 7 - CHANNEL ARCHITECTURE IN THE CONSTANT-FRACTION DISCRIMINATOR MODE                                     |       |

| FIGURE 8 - CFD SIMULATION SHOWING CFD EQUATION VERSUS DISCRIMINATOR BIT FROM LEADING-EDGE ARMING DISCRIMINATOR. | 14    |

| FIGURE 9 - PILEUP COUNTER OPERATION FROM SIMULATION OF FIRMWARE OPERATION.                                      |       |

| FIGURE 10 - USE OF DELAY BUFFERS M2, K AND K0 TO FORM PILEUP DELAY IN THE LEADING-EDGE MODE                     |       |

| FIGURE 11 - USE OF DELAY BUFFERS M2, K AND KO TO FORM PILEUP DELAY IN THE CONSTANT-FRACTION MODE                |       |

| FIGURE 12 - PILEUP OPERATION, WITH HORIZONAL AXIS SCALED TO ACTUAL TIME.                                        |       |

| FIGURE 13 - THE PEHQ AND PENDING EVENT QUEUE (PEQ) AS RELATED TO THE CHANNEL PIPELINE.                          |       |

| FIGURE 14 - RELATIONSHIP BETWEEN PIPELINE, PEHQ, PEQ AND EVENT HEADER FIFO.                                     |       |

| FIGURE 15 - TIMING OF EVENT EXPIRATION                                                                          |       |

| FIGURE 16 - EXTERNAL DISCRIMINATOR SELECTION LOGIC OF ONE CHANNEL.                                              | 23    |

| FIGURE 17 - SIGNAL DELAYS AND LOGIC OF TIMING MARKS IN THRESHOLD DISCRIMINATOR (LED) MODE.                      | 28    |

| FIGURE 18 - SIGNAL DELAYS AND LOGIC OF TIMING MARKS IN CONSTANT-FRACTION (CFD) MODE                             |       |

| FIGURE 19 - TIMING MARKS IN WAVEFORMS AS DISPLAYED IN GAMMAWARE.                                                |       |

| FIGURE 20 - GAMMAWARE DISPLAY SHOWING BOTH TIMING MARKS AND DELAY BUFFER SIZES OVERLAID UPON WAVEFORM           | 29    |

| FIGURE 21 - APPROXIMATE POSITIONS WHERE EARLY PRE-RISE SUMS ARE CAPTURED                                        | 31    |

| FIGURE 24 - EVENT TAKEN AT DOWNSAMPLE FACTOR OF 2, THUS SPANNING 2^2 CLOCK TICKS (40NS) PER SAMPLE ERROR! BOOI  |       |

| NOT DEFINED.                                                                                                    |       |

| FIGURE 25 - EVENT TAKEN AT DOWNSAMPLE FACTOR OF 2, IN THE ON-OFF MODE, WITH DOWNSAMPLE HOLDOFF OF 255           | RROR! |

| BOOKMARK NOT DEFINED.                                                                                           |       |

| Figure 22 - Trigger windows within the digitizer                                                                | 35    |

| FIGURE 23 - SUMMARY DESCRIPTION OF ALL FLAG BITS WITHIN THE HEADER.                                             | 38    |

| FIGURE 26 - PRE- AND POST-RISE ACCUMULATOR LOGIC                                                                | 44    |

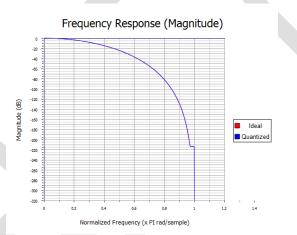

| FIGURE 27 - ESTIMATED FREQUENCY RESPONSE PLOT OF DIGITAL LEADING-EDGE DISCRIMINATOR FILTER.                     | 46    |

| FIGURE 28 - DISCRIMINATOR HOLD-OFF SET FAR SHORTER (200NS) THAN RISE TIME (~1US) - MULTIPLE HITS PER RISE       | 46    |

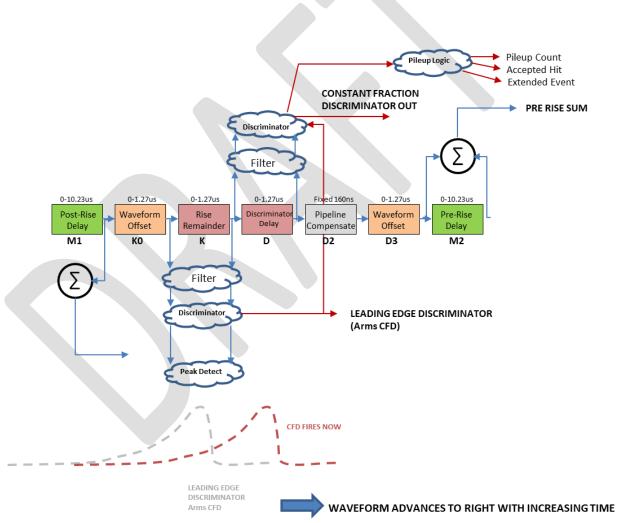

| FIGURE 29 – DISCRIMINATOR AND ENERGY SUMMATION PORTION OF CHANNEL LOGIC (CFD MODE).                             | 49    |

| FIGURE 30 - SCREEN CAPTURE FROM GAMMAWARE SHOWING POSITIONS OF BUFFERS IN CFD MODE                              | 50    |

| FIGURE 31 - EVENT READ OUT FULL SPEED (LEFT) AND DOWN-SAMPLED BY 8X (RIGHT)                                     | 53    |

| FIGURE 32 - EXAMPLE WAVEFORM FOR DESCRIBING PILEUP READOUT MODES                                                | 55    |

| FIGURE 33 - VISUAL REPRESENTATION OF THE READOUT MODES WITH PILEUP EXTENSION DISABLED                           |       |

| FIGURE 34 - VISUAL REPRESENTATION OF THE READOUT MODES WITH PILEUP EXTENSION ENABLED                            |       |

| FIGURE 35 - TRIGGER WINDOWS WITHIN THE DIGITIZER                                                                | 62    |

| FIGURE 36 - CONNECTIONS BETWEEN MASTER AND SLAVE DIGITIZERS                                                     | 65    |

### Introduction

This document is intended for users of the experiment setups at ATLAS who will be working with the firmware and adjusting parameters; a separate document, *Waveform Digitizers at the ATLAS experiments*, is available for those interested in a general overview of the digital data acquisition systems without reference to technical details. This document presupposes that the reader is already familiar with the overall design of the firmware and associated terminology.

### **Details of each channel**

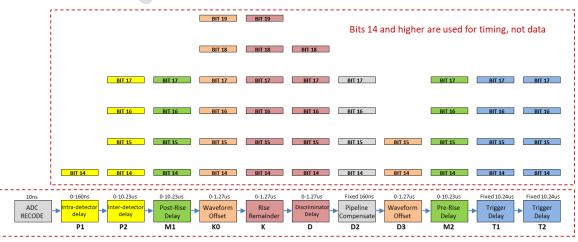

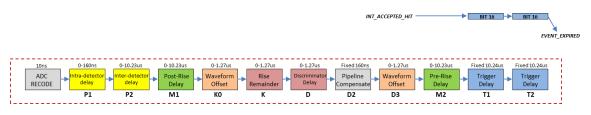

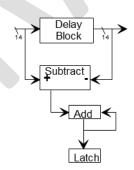

The 10 channels of the firmware are implemented as continuously running data pipelines. The structure of each channel is based upon the use of multiple delay buffers of varying width. Many of the timing functions of the firmware are based upon these delay settings. Xilinx FPGA logic cells implement small (16x1) RAM blocks that can also be configured as shift registers where the four input bits are then used as the length of the shift register. Similarly, Xilinx FPGA block RAM elements have parity bits that can be used for any general purpose. Both these features enable the designer to craft delay lines for single bits that are the same length as the delay buffers using far fewer FPGA resources than traditional counter-based delays. The delay buffer structure of each channel as implemented in shown in Figure 1.

The data path is 14 bits wide (bits 13:0) throughout

Figure 1 - Delay buffers per channel have differing widths for implementation of delays without counters.

#### Memory Structures within Xilinx FPGAs

The Xilinx FPGA implements two forms of memory resources, the **Block RAM** and **Distributed RAM**. All RAM within a Xilinx FPGA is dual-port in nature. Block RAMs are 18kbit units that may be reconfigured into a few standard sizes (1Kx18, 512x36, etc.). The bit-width of all Block RAM implementations is based upon a parity memory so that there are always a multiple of nine, rather than eight, bits of width. Most of the time these extra bits are ignored but as they are inherent to the Block RAM architecture they may be used to carry data

unrelated to the other bits so long as common clocking is acceptable. On the downside, Block RAM is scattered throughout the chip in fixed areas so as more and more of the Block RAM is used, it becomes increasingly difficult to route signals to those Block RAMs that remain. Many designs fail to route not because the chip is full, but because the design tries to use every Block RAM and the router software cannot find paths to every RAM at the speed required.

Distributed RAM memory uses the actual memory of the many logic slices of the FPGA itself. Every logic slice within the FPGA implements small 16x1 memories to perform the basic logic functions (AND, OR, etc.) as it is more efficient to simply use a small lookup table than to implement hard gates. This distributed RAM may be ganged together in small units to replace Block RAM and has the placement advantage of always being physically near the logic that wants to use it. Additionally, unlike block ram, the width of distributed structures is arbitrary. The downside of distributed RAM is that it requires some logic to gang together so sizes above 128x16 are usually impractical.

When implementing a delay structure as opposed to a general-purpose dual-port memory, the Distributed RAM may be further optimized by specific shift register macros named "SRL" in the Xilinx literature. These SRL macros use special internal connections available within the 16X1 distributed RAM buffer to "rewire" the RAM into a 16-element shift register. Data enters at position 0 and any one position may be brought out as the output. Serially ganging these SRLs together – assuming interconnect delays between them can meet timing constraints – allows arbitrarily long delay buffers to be implemented. As the SRL method does not require the address counters necessary in a generic dual-port RAM implementation, the SRL methodology provides very significant resource utilization reductions.

In the digitizer module, the actual ADC data is only 14 bits wide; thus, if a mix of Distributed RAMs (of any width desired) and 1Kx18 Block RAMs is used, there are four bits available for timing purposes across the entire delay chain. As most timing parameters are associated with the buffer lengths use of these extra bits to form state machine delays is highly efficient. The normal method by which this is done is to have a state machine generate a pulsed signal one clock period wide at the start of a delay state that is connected to the input side of a delay buffer. The state machine then waits for the delayed copy of the bit to fall out of the other side of the delay buffer before proceeding or branching. Resources needed to implement a delay counter are eliminated and comparison logic is reduced to a single bit. While this may not seem like much, multiplied over 10 channels with multiple delays per channel results in a significant fraction of the FPGA's resources being conserved.

#### Important FPGA generalities

Within Xilinx FPGAs all logic must be formed from cells called CLBs (Configurable Logic Blocks). All CLBs consist of a small lookup memory with four inputs and one output (thus a 16x1 RAM) that implements all gate-level logic and a D flip-flop. There are no AND, NAND, OR, NOR, XOR or NOT gates inside; all asynchronous logic is formed from the 16x1 RAMs. Similarly, there is no such thing as a set-reset (SR) latch in an FPGA; there are only D flip-flops.

Collections of D flip-flops that work synchronously on a group of bits interpreted as a value, but that have no connection to software programs outside the FPGA, are called *latches* throughout this document. This is to differentiate them from *registers*, that are constructs of software outside the FPGA used to load control values to or read status values from the FPGA. Obviously, *registers* are formed out of D flip-flops too, but to understand the timing of firmware operations there must be a distinct term for the internal objects that sample data values within state machines or pipelined signal processing chains. The word *latch* should imply "D flip-flop inside the FPGA" whereas *register* should imply "D flip-flop that connects outside the FPGA".

The design of the CLB must be understood to mean that every D flip-flop in the FPGA has a built-in multiplexer at the input. Additionally, the D flip-flop in every CLB has a *clock enable* term that allows it to only sample on some clocks, not all. Because of this, the word *latch*, when used in any drawing within this document, *should not be misinterpreted to be an object that can only have one input*. A drawing object identified by the word 'latch' with multiple inputs simply means that the built-in multiplexer is being used and that this particular set of D flip-flops can sample different input data at different times or under different conditions.

#### **Channel Initialization**

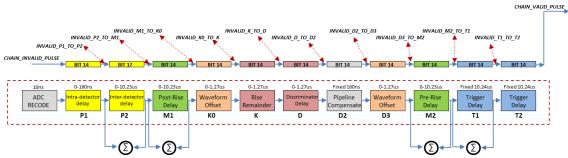

The various running sums used in the ANL firmware require proper initialization, as do all functions based upon delays. The firmware design allows the user to load all channel delay parameters into the registers of the module in any order desired without affecting channel pipeline operation. After all new parameters are loaded a single, final, write to a pulsed control register (a register that creates a one-clock-wide pulse in response to a '1' being written to a bit in the register irrespective of control interface speed) called *LOAD\_VALS* causes a self-timed sequence of initialization throughout the length of the channel pipeline. This is shown in Figure 2.

Figure 2 - Timing of CHAIN\_INVALID and sequenced initialization thereafter.

In response to the *LOAD\_VALS* signal another signal CHAIN\_INVALID\_PULSE is generated that enters the pipeline at the input to buffer P1 and proceeds throughout the pipeline until exiting at the other end. The immediate response to *LOAD\_VALS* is to reset the length of all delay buffers to their new values, after which CHAIN\_INVALID\_PULSE enters the pipeline. The various tap delays of CHAIN\_INVALID\_PULSE initialize the energy sum logic at the appropriate times:

- The sums across P2, M1 and M2 are held at zero until INVALID\_P1\_TO\_P2 goes high, at which point the sum across P2 starts adding.

- When INVALID\_P2\_TO\_M1 goes high, the sum across P2 starts tracking and the sum across M1 starts adding.

- When INVALID\_M1\_TO\_K0 goes high, the sum across M1 starts tracking.

- When INVALID\_D3\_TO\_M2 goes high, the sum across M2 starts adding.

- When INVALID\_M2\_TO\_T1 goes high, the sum across M2 starts tracking.

There is a distinction between similarly named signals CHAIN\_INVALID, CHAIN\_VALID\_PULSE and CHAIN\_INVALID\_PULSE. When *LOAD\_VALS* is asserted, CHAIN\_INVALID and CHAIN\_INVALID\_PULSE both are asserted, but CHAIN\_INVALID\_PULSE lasts for only a few clock ticks. CHAIN\_INVALID, once set, stays set for the entire time it takes CHAIN\_INVALID\_PULSE to propagate through all the delay buffers until CHAIN\_INVALID is reset by CHAIN\_VALID\_PULSE. CHAIN\_INVALID is therefore on for the entire duration of the initialization of the pipeline but the various tap delays of CHAIN\_INVALID\_PULSE are short pulses that occur in sequenced delays after *LOAD\_VALS*.

#### **Best initialization practice**

During the initialization sequence an internal bit vector SUBSECTION\_RESETS(9:0) is set to "111111111" when *LOAD\_VALS* is asserted. The reset vector is held at "111111111" until the signal *CHAIN\_VALID\_PULSE* falls out the end of the pipeline. At this point, zeroes are shifted into SUBSECTION\_RESETS from bit 0 towards bit 9 every tick of the clock until the vector becomes "0000000000". Different bits of the reset vector control different processes within the channel logic (e.g. discriminator, pileup, etc.) so that the order of release can be controlled.

So long as SUBSECTION\_RESETS(9) is high, the **ADC\_RECODE** block is held in a state where the input is held constant at a value the user stores in a register. When the reset bit is released normal ADC values are allowed in. This ensures that the energy sums all start with 'n' times this initialization value (where 'n' is the length of each buffer) and then track from that point to the sum of real data after the chain is released. Thus for best operation, the user should take some test waveforms to estimate the baseline ADC value of the channel in normal operation and set the initial value register for each channel to that estimated baseline value so that there's not a large false step in the data that may be interpreted as a discriminator edge. As a secondary safeguard the threshold discriminator logic state machine is designed to ignore the first edge after reset, should the user fail to set the initial value register appropriately.

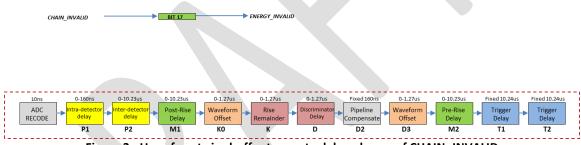

However, since the energy sums are tracking objects, they still require time to track to appropriate values after being released. This can take up to ~25us based upon user settings for the delay buffers. A secondary signal named ENERGY\_INVALID, based upon the signal CHAIN\_INVALID, is created using the post-rise delay buffer to further disable the threshold discriminator by the length of the post-rise sum buffer after *CHAIN\_VALID\_PULSE* is asserted, as shown in Figure 3. This, plus the ignorance of the first edge after release of the threshold

discriminator, should guard against any erroneous energy sums in the first event after reset release under most circumstances.

Figure 3 - Use of post-rise buffer to create delayed copy of CHAIN\_INVALID

### **Specifics of discriminator operation**

The firmware implements two forms of discriminator logic in every channel, *leading-edge* and *constant-fraction*. Each channel may be individually configured for mode and polarity of discriminator operation. There are *two* discriminator functions in every channel, an early, unfiltered one called the *coarse discriminator* and the *main* discriminator. Only the *main* discriminator can be operated in both modes; the *coarse* discriminator always operates in leading-edge mode. While the *coarse* discriminator has its own threshold setting, the depth of its delay buffer cannot be changed, and the polarity is constrained to be the same as that of the main discriminator.

The purpose of the *coarse* discriminator is to create a signal with minimum delay so that a fast multiplicity trigger may be generated by Digital Gammasphere for use with auxiliary detectors that do not have the ability to buffer events. As the coarse discriminator provides an "early warning" signal well before the edge reaches the main discriminator logic, the firmware as of August 2021 also uses the coarse discriminator to capture additional copies of the sum across the pre-rise buffer at times before the main discriminator can fire.

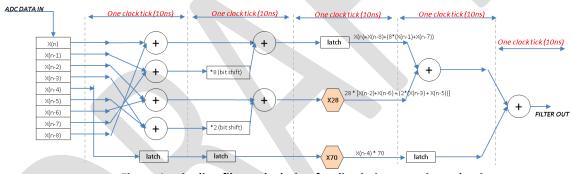

The main discriminator uses a digital filter to reduce noise. This filter is based upon the simple filter function Y(n) = X(n) + (2\*X(n-1)) + X(n-2). If this filter is convoluted four times the resulting equation is

$$Y(n) = X(n) + 8 * X(n-1) + 28 * X(n-2) + 56 * X(n-2) + 70 * X(n-3) + 70 * X(n-4) + 56 * X(n-5) + 28 * X(n-6) + 8 * X(n-7) + X(n-8)$$

This is implemented in the firmware in a pipelined process that requires multiple clocks to solve, but comes up with a new answer every clock, as shown in Figure 4.

Figure 4 : pipeline filter calculation for discriminator noise reduction.

The ADC samples entering the K buffer, between the K buffer and the D buffer, and exiting the D buffer are sent through three copies of this filter. A multiplexer routes the appropriate two copies to the leading-edge discriminator block depending upon the discriminator operating mode. Since the sum of the coefficients of this filter equals 256, the lower 8 bits of the FILTER\_OUT value are discarded so that FILTER\_OUT, as used in discriminator logic, is still a 14-bit number to match the ADC raw data.

#### Operation in the leading-edge discriminator mode

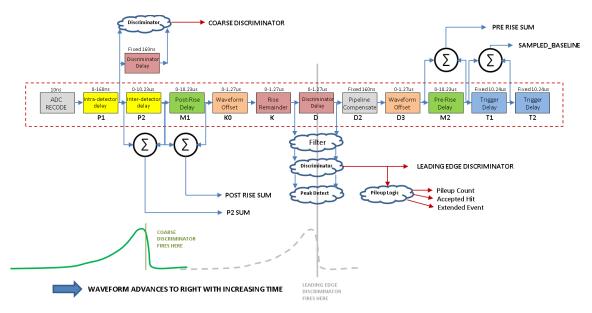

An overall picture of the channel pipeline in the simpler threshold, or leading-edge, discriminator mode is shown in Figure 5.

Figure 5 – Channel architecture in the leading-edge discriminator mode.

The two outputs of the two selected filter chains are processed by a discriminator state machine. This state machine subtracts the "delayed" input (the input on the right side, that has

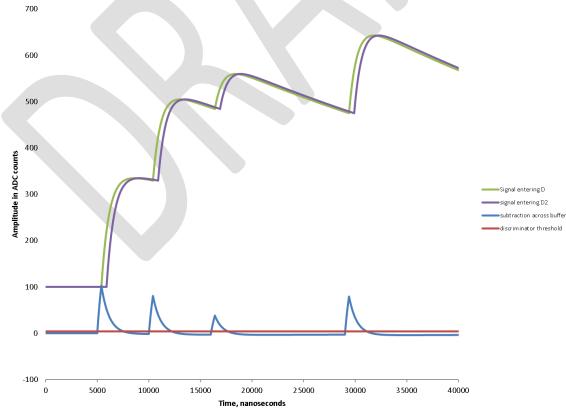

more delay from the ADC than the one on the left) from the "prompt" input (the input on the left side, that has less delay from the ADC than the one on the right) every 10ns. For a positivegoing pulse this means that the resulting value will become larger as the signal rises. This difference is compared against a discriminator threshold every 10ns, and if the difference exceeds the threshold the discriminator fires. This means that the leading-edge discriminator is a discriminator of *slope*, not a discriminator of *level*. A calculated simulation of this running subtraction over time is presented as Figure 6.

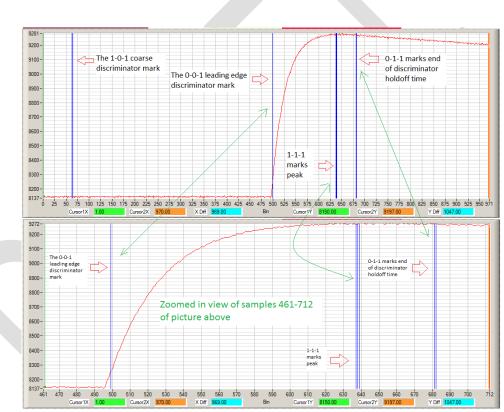

Figure 6 - simulation of leading-edge discriminator operation.

The amplitude of the subtraction is dependent upon the length of the 'd' buffer plus the slope of the edge of the signal. A larger 'd' allows the firmware to sense smaller amplitude and/or slower rise time signals. Conversely, a smaller 'd' exhibits less time walk. As a practical matter, a value of 'd' less than 10 is likely to result in non-optimal operation from numerical truncation error in the subtraction. For HPGe detectors with a rise time of less than 1usec, a 'd' value of 16 is recommended. For these reasons, the delay buffer of the coarse discriminator uses a fixed delay time of 160ns (16 clocks).

#### **Discriminator Hold-off**

Referencing Figure 6, the threshold level is exceeded for many clocks once crossed. The leading-edge discriminator avoids multiple firings by implementing a *discriminator hold-off* value, stored in a control register. On the first tick of the clock when the threshold is crossed, a counter is loaded with the hold-off count, and for that many ticks of the clock the leading-edge

discriminator is disabled so that it only fires once per edge. The hold-off time is a function of the rise time of the signal and should be set by the user appropriately for the input signal characteristics. The discriminator output signal used by other portions of the logic is a pulse 10ns wide (one clock) that occurs on the first clock after the threshold is crossed. The hold-off logic ensures that this pulse only occurs once for each input edge.

#### **Preamp Reset Kill**

The firmware implements a function akin to hold-off named Preamp Reset Kill. The Gammasphere detectors use *transistor-reset* preamplifiers. This type of preamplifier continuously integrates charge from detector leakage current resulting in an output signal that looks like a slow ramp over many milliseconds. A comparator within the preamplifier detects when the ramp has reached the limit of the analog circuitry at which point a transistor turns on to bleed off all the accumulated charge resulting in a large amplitude, fast recovery. Over period of seconds these resets look like a sawtooth waveform. The detector signals of interest are much smaller steps overlaid upon this long term sawtooth.

The interface circuitry of Digital Gammasphere (the Slope Box Extension, or "SBX") implements a differentiator circuit between the preamplifier and the digitizer such that the signals of interest become exponentially shaped signals. This has the effect of turning the preamplifier resets into very large exponentials of the opposite polarity of the signals of interest. The SBX implements a fast-acting clamp circuit that greatly limits the excursion and duration of these reset signals, but the clamp cannot eliminate them. This results in an opposing polarity signal of large amplitude, followed by a fast edge returning to baseline, followed by a period during which the clamp is on in which the exponential decay time constant of detector signals is far shorter than normal.

During the reset and the duration of the clamping time measurements of energy are distorted. The Preamp Reset Kill function, if enabled by setting a bit in the channel control register, implements another version of discriminator with large, preset threshold and opposite polarity to the main & coarse discriminators. When this circuit detects a Preamp Reset, it starts a delay count. While the delay is in progress the main discriminator is disabled preventing response to both the Preamp Reset recovery signal and the distorted detector signals.

In Gammasphere the Preamp Reset occurs at rates of once every few milliseconds to once every few hundred milliseconds depending upon how much neutron-induced damage the detector has. The SBX clamping time is normally on the order of 200-250 microseconds, so the dead time percentage introduced by Preamp Reset Kill is not significant until the detector is near the point at which it must be removed from the array and annealed.

#### **Peak Detector**

Inside the leading-edge discriminator machine, when the discriminator fires the filtered ADC value at the "prompt" input to the discriminator is saved. On every tick of the clock thereafter, the "prompt" value is compared to the saved value. If the "prompt" value is still climbing (or, if discriminator is set for negative edges, still falling), the saved value is updated

with the "prompt" value. The saved value continues to rise (or fall) as the signals rises (or falls) towards its maximum.

There is noise in every physical system, so the peak detector implements a filter called the *peak sensitivity* value. The *peak sensitivity* value is the number of clocks in a row that the saved value is **not** updated before the peak is declared. A usual value for this parameter is 4, meaning that if the saved value hasn't been updated for four clocks in a row the peak is found.

The peak detection process is also controlled by the holdoff time. If a peak is found before the holdoff time, the timestamp of the peak is saved for the header of the event and a bit in the header named PEAK\_VALID is set. If the holdoff time elapses before a peak is found, the timestamp of the peak will be reported as zero and the PEAK\_VALID flag will not be set.

Conversely, the user may set a bit in the channel control register that will terminate the hold-off time early once a peak is found. This can be useful if the rise time of the input signals varies; the hold-off time is set for the slowest pulses, but terminates early for the faster pulses, resulting in the discriminator always re-arming at the earliest possible time.

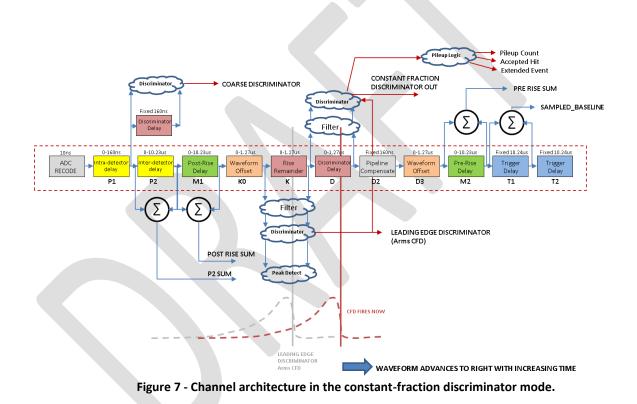

#### Difference in operation of the Constant-Fraction mode

The channel design is slightly changed in when constant-fraction mode is enabled, as shown in Figure 7. The leading-edge discriminator logic moves forward one delay block to span delay buffer "k", and the center delay "d" is now monitored by the constant-fraction discriminator (CFD). The leading-edge discriminator is used to gate the operation of the CFD, to avoid false firings. The leading-edge discriminator fires as the leading edge of the waveform passes through the "k" buffer. The CFD logic starts calculating when the leading-edge discriminator fires, and the CFD itself fires when the CFD equation at the selection fraction is satisfied.

All three filter elements are used in CFD mode, with the output of the middle filter connected to the leading-edge discriminator as the "delayed" input and also to the constant-fraction discriminator as its "prompt" input. The CFD state machine is normally in an idle state and waits for the leading-edge discriminator to fire before it begins calculating. Calculations continue until the CFD logic is satisfied or until the leading-edge holdoff time elapses, whichever comes first.

Figure 8 - CFD simulation showing CFD equation versus discriminator bit from leading-edge arming discriminator.

An important observation regarding Figure 8 is the varying level of the CFD equation for the different pulses. When the leading-edge discriminator fires, the level of the CFD equation *at that time* is saved as a value LOCAL\_ZERO. The CFD state machine, once armed, calculates the CFD equation and subtracts from that the value of LOCAL\_ZERO. Note that in Figure 8 the "leading edge arming" signal has no relationship to the Y axis. The "leading edge arming" is arbitrarily scaled to highlight the times when the CFD calculation is sampled to save LOCAL\_ZERO. The sign of that subtraction is saved on the first clock that the CFD state machine runs, and the CFD firing is declared when the sign of (CFD\_equation – LOCAL\_ZERO) changes. This results in consistent CFD operation even as the DC level of the CFD equation wanders about due to the presence of other pulses – even during pileup.

#### Time interpolation using the CFD Sample values

Three CFD Sample values are provided in the CFD-mode header to allow interpolation of the timestamp. The CFD equation  $[X_{(n)} * fraction] - X_{(n-d)}$  for a positive-going pulse is expected to rise and then plummet through zero to a negative value as the input passes the fractional percentage value desired. The CFD Sample values are the values of the CFD equation at the clock tick when the timestamp is latched, the sample one clock tick earlier and the sample two clock ticks earlier. The expectation is that there will be two positive samples and one negative sample captured for a positive-going input pulse.

These three values are entered into a linear regression and the intercept (where the fit line equals zero) determined. The non-zero fractional 'x', or time, value at Y=0 is subtracted from the timestamp reported to obtain the interpolated timestamp. The accuracy of the interpolation method is highly dependent upon the rise time of the incoming signal, and secondarily dependent upon the amplitude of the incoming signal. This is simply because the CFD timing accuracy is proportionate to the slope of the effective differentiator, so faster rising inputs yield a greater slope and thus less time (x) error. At small signal/noise ratios the fit gets "fuzzy". Test stand results obtained using signals with 800-1000ns rise times are a 1-sigma normal distribution of interpolated time results of about 1.7ns for relatively large signals, degrading to a 1-sigma of about 2.5ns for tiny signals at the limits of leading-edge discriminator detection.

#### **Detecting improper CFD operation**

For very closely spaced pulse pairs it is possible that the hold-off time set for the leading-edge discriminator may fall during the rise of the second pulse, such that the 'local zero' value of the CFD equation is latched late. In this case the CFD equation may fire but not at the desired fraction of the pulse. The risk of this can be minimized by using the early termination of the hold-off time when the peak is found. Events in which the 'local zero' has been sampled at a late time are normally identified by examining the sign of the three CFD interpolation samples. All correct CFD firings will have the sign of the first two samples the same with the third either being zero or of the opposite sign of the first two. Erroneous 'local zero' sampling typically results in all three CFD interpolation samples having the same sign.

#### **Details of Pileup Logic**

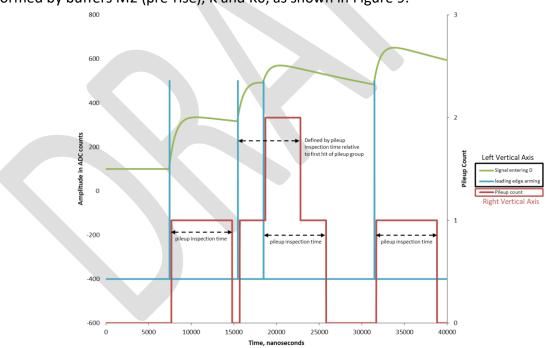

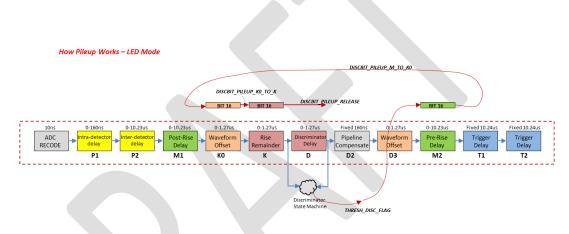

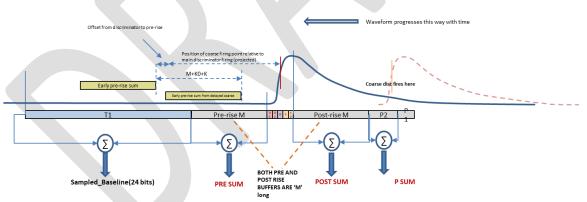

Pileup is based upon a counter that increments every time the discriminator fires and decrements every time that a delayed copy of the discriminator bit falls out of a delay chain formed by buffers M2 (pre-rise), K and K0, as shown in Figure 9.

Figure 9 - Pileup counter operation from simulation of firmware operation.

The counter is incremented when the discriminator fires and decrements when a copy of the discriminator bit, delayed by the pileup inspection time 'm'+'k0'+'k', exits the delay chain. This is shown in Figure 10. Since the delay chain is a long shift register, this means that there can be an arbitrary number of 1s in the delay chain; the limiting factor is the discriminator holdoff time. A secondary limiting factor is that the pileup counter is only four bits, so there is another limit of no more than 15 discriminator hits during the pileup inspection time. In this exceptional case, since the pileup counter has overflowed, the channel pileup logic will seize up into a *pileup overflow* state. This state is detectable by reading status bits in the master status register, requiring software or user intervention to reset the channel logic and the pileup counter. With HPGe detectors using an 'm' of 6us, the counter limit sets the maximum hit rate at one hit every 400ns, twice as fast as the typical rise time of HPGe signals. A properly set holdoff time ending at or near the peak will ensure no pileup counter overflow.

Figure 10 - Use of delay buffers M2, K and K0 to form pileup delay in the *leading-edge* mode.

The picture is the much the same in CFD mode. As shown in Figure 11, the pre-arming leadingedge discriminator moves to look at the signal across 'k' rather than 'd', but the pileup timing remains the same. The reason behind this is that the leading-edge discriminator **must** work for the constant-fraction discriminator to work, but if the user sets incorrect CFD parameters it is possible for the leading-edge to fire but the constant-fraction to sometimes fail. Thus, it is safer to always base pileup timing upon the leading-edge discriminator.

Figure 11 - Use of delay buffers M2, K and K0 to form pileup delay in the constant-fraction mode.

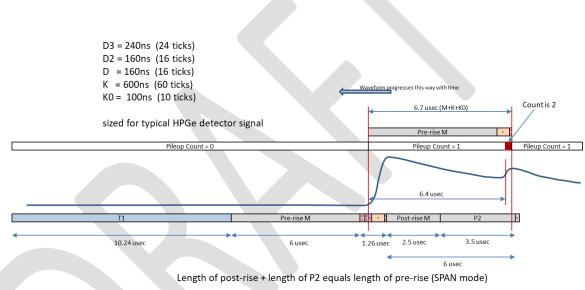

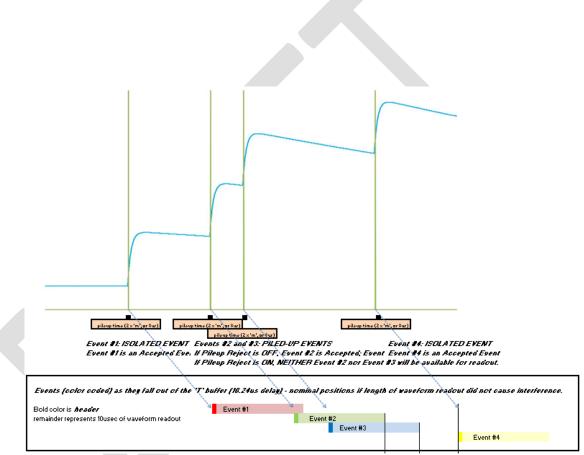

A properly scaled diagram of a waveform relative to these buffers relative to a handsketched waveform provides a bit more context. In Figure 12, the waveform and the buffers are shown in "oscilloscope view" to ease understanding; the order of the delay buffers is reversed left-right relative to previous pictures. The first edge of the waveform is shown aligned with the edge of the 'd' buffer as would be the case using the threshold discriminator. A minor adjustment relative to actual firmware construction, to simplify the drawing, shows the edge aligned with the left edge of 'd'. In actuality, the filter and discriminator logic require a few clocks to function, so by the time the discriminator bit fires, the waveform would be at the left edge of 'd2'; but for simplicity we will ignore that delay as it occurs on both sides of the pileup equation and cancels out for the purposes of Figure 12.

Figure 12 - Pileup operation, with horizonal axis scaled to actual time.

At the time of the discriminator firing for the first edge the pileup counter increments from 0 to 1. This enters the delay buffer chain shown in Figure 4 as "DISCBIT". The discriminator fires a second time 6.4usec later, incrementing the pileup counter from 1 to 2. 6.7usec after the first edge the counter decrements from 2 to 1, and another 6.7usec after that (outside of picture) the pileup counter would again decrement from 1 to 0.

It is important to note here that *Discriminator Hits* become *Accepted Hits* based upon the value of the pileup counter *when the DISCBIT\_PILEUP\_RELEASE bit associated with the hit falls out of the delay buffer.* This means that the *first* hit in the "train" of piled-up hits *has been marked as piled upon before it is potentially accepted* **plus** *every piling-on hit is also marked as being in pileup.* The readout logic uses the **value** of the pileup counter to differentiate the *first* hit in a pileup train from all the other hits in the same train, marking the *second* and all following as *Extended Events* (if accepted), as opposed to the *first*, that if accepted becomes the *Accepted Hit*.

#### Handling of Pileup

The firmware may be set to either accept or reject pileup. If pileup is allowed, many different readout options are available that handle pileup in different ways; this will be discussed later in this document when the focus changes to the readout logic. If pileup rejection is enabled, then all *discriminator hits* that are in pileup are discarded. When pileup rejection is in play, *discriminator hits* not in pileup become *accepted hits* and there can be no *extended events*.

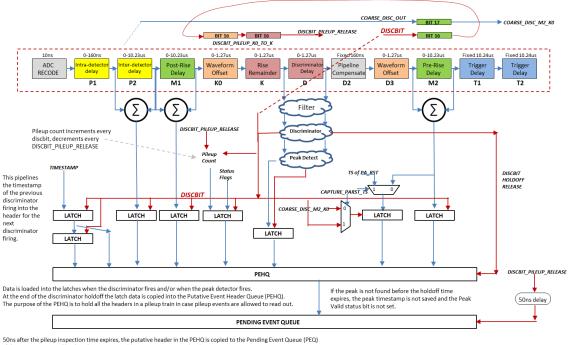

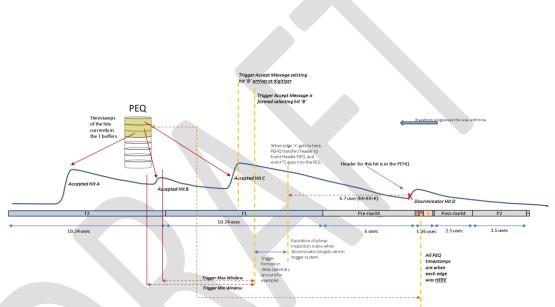

#### Relationship of pileup to event header formation

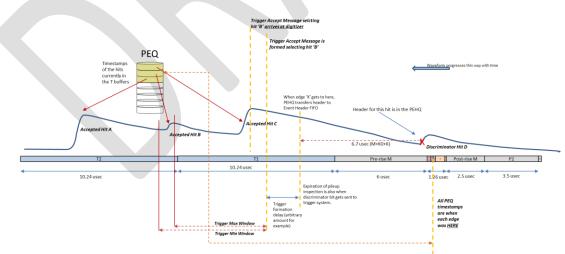

Event headers are captured by the digitizer firmware in stages. This timing is critically important to understanding the full operation, so please read carefully.

At the time of the discriminator firing, most of the data in the header is known, but not everything. A very wide latch captures most header information (timestamp, energy sums, etc.)

when the discriminator fires. During the time of the discriminator holdoff, this latch can accumulate additional information, so if a peak is found after the discriminator fires, the timestamp of the peak and/or its value can also be saved in this latch. At the time the discriminator holdoff expires, the data in this latch is copied to a short but wide FIFO called the Putative Event Header Queue, or PEHQ.

Extreme care with terminology is required here. The PEHQ data is named putative because at the time the PEHQ is written, the data in the PEHQ may or may not survive to become an Accepted Hit because at that moment the pileup status is not yet known. Typically, the discriminator holdoff time is set to something around 1.5usec. Referring to Figure 12, this time is much shorter than the pileup inspection time, calculated earlier to be 6.7us. The putative header is loaded into the PEHQ 1.5 usec after the discriminator fires (holdoff time) but until the 6.7us pileup inspection time expires the pileup status will not be certain. The *putative* header resides in the PEHQ for that 5.2 usec. A second header is loaded into the PEHQ 6.7 usec after the first one, so in the example of Figure 5 there's never more than one event in the PEHQ. However, for longer values of 'm' combined with short holdoff times multiple putative headers could be in that buffer simultaneously. For example, with 'm' = 10.24 usec combined with a faster input signal that only needs a 'k'+'k0' of 400ns (resulting in a likely holdoff time of ~1usec) there could be 10 events in the PEHQ if the hits come in a fast sequence just slower than the holdoff time would block. The PEHQ has a depth of 16, so should be capable of withstanding almost any normal experimental situation. See Figure 13.

If the event is accepted by the pileup processor (that is, it is an Accepted Hit). Only the Accepted Hits enter the PEQ for possible selection by the trigger for readout. The other headers in the PEHQ (Extended Events) get copied from the PEHQ into the Event Header FIFO depending upon the readout mode selected. If the readout of any Extended Event does not occur due to Readout Interference or because the mode does not use them, every DISCBIT PILEUP RELEASE the Extended Event is popped off the PEHO so that the PEHO never fills

Figure 13 - The PEHQ and Pending Event Queue (PEQ) as related to the channel pipeline.

#### **PEHQ latch timing requirements**

The PEHQ **latch** must collect information starting "sometime" before the discriminator fires (i.e. the "early" pre-rise energy sums), and must finish collecting before the end of the holdoff time (because that's when the latch is written into the PEHQ). However, the different items within the PEHQ become valid at different times within the event. The PEHQ latch solves this by writing and re-writing certain latch values using different signals derived from the various state machines. The *clock* to all latches in the PEHQ is the 100MHz clock that runs continuously, but the *clock enable* to any given portion of the PEHQ latch may occur zero, one or multiple times during the formation of the event.

For example, one latch in the PEHQ holds the CFD\_VALID bit that comes out in the header. That latch is loaded with '0' every time the leading-edge discriminator fires, but a separate clock enable term allows a '1' to be written if later the CFD fires.

The majority of PEHQ latch items are loaded when the leading-edge or constant-fraction discriminator fires, but some latches load at other times. The "early pre-rise energy" header value is sampled when the coarse discriminator fires, well before the main discriminator bit can occur. Similarly, a *delayed* copy of the coarse discriminator bit is used to capture a *third* copy of the pre-rise buffer sum 'm' + 'k0' *after* the coarse discriminator fires, a time that will be close to the timing of the main discriminator but still reliably before then. Because the timing of the coarse discriminator, there must also be a latch that captures some bits of the timestamp count when the coarse discriminator fires so that the delta-t between these early pre-rise sums and the normal pre-rise sum can be calculated for every event. Another example of this is the timestamp of the peak, that obviously must be sampled only when the peak is found.

Effectively, then, the PEHQ latch begins collection when the holdoff time of event(n) occurs, and collection ends when the holdoff time of event(n+1) occurs. With real signals, this is a variable number.

#### Holdoff time versus pileup time

Since the PEHQ latch gets written to the PEHQ at the end of the holdoff time, and the PEHQ is unloaded at the end of the pileup inspection time ('m'+'k0'+'k'), there is a requirement that *the holdoff time must always be shorter than the pileup inspection time*. If this is violated, the PEHQ underflows and the digitizer firmware cannot function. To avoid this condition, the firmware implements a "pileup too short" process that will set an error bit PU\_TIME\_ERROR\_FLAG if the pileup time is shorter than the holdoff time. If this bit is set the readout logic is prevented from operating, causing there to be no data from the digitizer. A bit in a status register is also set when this condition occurs.

The condition prevents digitizer operation, and the only way to resume operation is to adjust the holdoff and/or pileup time to meet the requirement and then re-initialize all

channels. A complete power cycle reset is not required, just a soft reset of the logic in all channels will suffice.

#### Event Formation at the end of the pileup inspection time

When the pileup inspection time elapses after a discriminator hit, two things happen.

- The *putative* header stored in the PEHQ <u>may</u> be transferred into the Pending Event Queue (PEQ), becoming an Accepted Hit, depending upon whether pileup events are allowed or not, and

- 2. The *Accepted Hit*, if formed, sets a discriminator bit that is transmitted to the trigger system for the formation of multiplicity triggers and for clean/dirty inspection.

In every channel the channel control register contains a bit that selects whether hits marked as pileup can become *Accepted Hits* or not. As noted previously only the *first* hit in a pileup train can become the *Accepted Hit*. The rest of the hits in the pileup train are accepted or rejected as a group based upon the selection applied to the first hit. As Figure 7 shows, there are two parallel paths of information after the PEHQ. The *timestamps* of the accepted hits enter the PEQ for possible selection by the trigger (thus changing from *accepted hits* to *accepted events*) whereas the header data from all hits (*accepted hits* and, if pileup is allowed, *extended events*) transfer from the PEHQ to the Event Header FIFO.

When pileup rejection is ON, no hit in a pileup train will become an *Accepted Hit*. The logic that transfers headers from PEHQ to Event Header FIFO uses *Accepted Hit* and/or *Extended Event* timing to both advance the PEHQ and write the Event Header FIFO.

- If pileup rejection is ON, the putative headers of the entire pileup train stored in the PEHQ are popped out of the PEHQ and never written to the Event Header FIFO at the end of the pileup inspection time.

- If pileup rejection is ON, Accepted Hits not marked as pileup <u>are</u> copied from PEHQ to the Event Header FIFO at the end of the pileup inspection time and simultaneously popped out of the PEHQ.

- If pileup rejection is OFF, all *Accepted hits* and *Extended Events* are copied from PEHQ to the Event Header FIFO, but still at the end of the pileup inspection time.

Figure 14 - relationship between pipeline, PEHQ, PEQ and Event Header FIFO.

#### Triggered modes vs. "Internal Accept All"

The Pending Event Queue is used only when the firmware is set to select events for readout based upon acceptance messages from the external trigger system. If the firmware is set to "internal accept all" the PEQ is bypassed, and all *accepted hits* immediately become *accepted events*. In the "TTCL" mode, a 2<sup>nd</sup> level of accept/reject of headers in the Event Header FIFO occurs at a time called **Event Expiry**.

#### **Event expiry**

An Accepted Event expires when the waveform data associated with the Accepted Event can no longer be read out. This timing is defined as the length of the Trigger Delay Buffer (T1 plus T2 viewed as a single delay element). See Figure 8. Every Accepted Hit inserts a 10ns wide pulse into the T1+T2 buffer set, that exits 20.48us later as **EVENT\_EXPIRED**. Since the hit is only consuming one of the 2048 cells of this digital delay buffer, many hits can be simultaneously active. Every tick of the clock, if **EVENT\_EXPIRED** is asserted, the Event Header FIFO is popped and the eldest event in the PEQ marked as no longer valid for selection. These actions render the event no longer available for readout.

Figure 15 - timing of event expiration.

The operation of the PEQ, with events loaded by *Accepted\_Hit* and events unloaded by *EVENT\_EXPIRED*, results in the PEQ always containing the list of timestamps of all events whose

waveform could be read out because they are still within the T1+T2 buffers (collectively referred to in other documentation as the *Trigger Delay Buffer*).

#### Event status bits in the PEQ

Every entry in the PEQ has, in addition to the timestamp of the discriminator, status bits including

- a three-bit placeholder for the trigger *type* as broadcast in the acceptance message from the trigger;

- a *pending* bit that marks the PEQ entry as "active" but not "selected".

- an *accepted* bit that marks the PEQ entry as "selected". PEQ entries with the *accepted* bit set should read out

- a *ReadOutMachineSignaled*, or "ROMS", bit that marks the PEQ entry as one that has been signaled to the readout logic.

An event in the PEQ whose *pending* bit was set but whose *accepted* bit was never set is simply one that dies because the trigger never selected it. No special action occurs in the PEQ at the time of *EVENT\_EXPIRY* other than the removal of the pending event from the queue. The PEQ does not in any way mark, cause or count *dropped events*; this is a function solely of the readout logic.

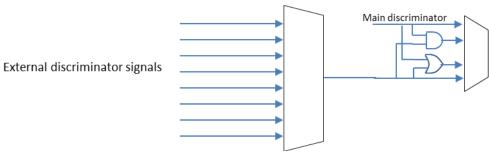

#### **External Discriminator Modes**

The digitizer firmware provides a selection of different *external discriminator* signals, of which **one** may be chosen as the *external discriminator source* per channel. Then a 2<sup>nd</sup> set of selection logic in each channel allows the user to select whether the *external discriminator source* signal is

- ignored

- ANDed with main discriminator signal (i.e. external *gates* the main)

- ORed with main discriminator signal

- is used *in place of* the main discriminator

This selection logic is shown in Figure 16.

Figure 16 - External discriminator selection logic of one channel.

One of the external discriminator signals is derived from the timestamp and is itself multiplexed to provide different periodic signals.

#### **External Discriminator Signals**

The selection of external discriminator signals varies slightly between channels, and also upon whether the digitizer is a "master" digitizer or a "slave" digitizer. The selection matrix is provided in Table x.

| External      | "Master" digitizer |            | "Slave" digitizer |             |             |             |

|---------------|--------------------|------------|-------------------|-------------|-------------|-------------|

| Discriminator | channel 9          | channels   | channels          | channel 9   | channels    | channels    |

| Select        |                    | 5-8        | 0-4               |             | 5-8         | 0-4         |

| 0             | '0'                | channel 9  | channel 9         | ·0'         | channel 9   | channel 9   |

| 1             | '0'                | '0'        | '0'               | ch. 9 of    | same ch.    | same ch.    |

|               |                    |            |                   | mstr dig    | of mstr dig | of mstr dig |

| 2             | front              | front      | front             | front panel | front panel | front       |

|               | panel              | panel      | panel             |             |             | panel       |

| 3             | TS bit             | TS bit     | TS bit            | TS bit      | TS bit      | TS bit      |

| 4             | VME                | VME        | VME               | VME         | VME         | VME         |

|               | command            | command    | command           | command     | command     | command     |

| 5             | '0'                | '0'        | if channel        | '0'         | '0'         | '0'         |

|               |                    |            | (n+5) is          |             |             |             |

|               |                    |            | killed by         |             |             |             |

|               |                    |            | Preamp            |             |             |             |

|               |                    |            | Reset             |             |             |             |

| 6             | command            | command    | command           | command     | command     | command     |

|               | from trig.         | from trig. | from trig.        | from trig.  | from trig.  | from trig.  |

|               | if                 | if         | if selected       | if selected | if selected | if selected |

|               | selected           | selected   |                   |             |             |             |

| 7             | any other          | any other  | any other         | any other   | any other   | any other   |

|               | channel            | channel    | channel           | channel     | channel     | channel     |

Table 1- External discriminator source matrix.

A few of the entries in Table 1 require additional explanation. The "front panel" option is an RS-485 input that is part of the Auxiliary I/O of the digitizer module. There are 11 bits of Auxiliary I/O on the front panel. The MSbit (AUX\_DIN[10]) is the bit used for external discriminator activity. The Auxiliary I/O connector has multiple modes of operation as described in a later section of this document; in some of them, bit 10 may be an output, not an input. In those modes the front panel bit cannot be used as part of external discriminator logic.

The "command from trigger if selected" entry means that there is a command that the trigger system can send during Frame 15 of the 20 frame trigger command cycle. When the trigger sends a non-null command in Frame 15, the command can have various command *values*, of which one value means "assert external discriminator bit". When this occurs, the command from the trigger will also contain a *selection mask* of which channels in the digitizer are to have their external discriminator bit asserted. This allows the trigger to selectively create

discriminator firings in different channels of every digitizer in the system for the purpose of verifying the cabling plant and all sources of multiplicity.

The VME command mode is like the trigger command mode but does not have system-wide synchronicity like the trigger command. The source of the external discriminator bit is from a write-only "pulsed control" register; only those channels set to this mode will receive the external discriminator signal. This mode is intended for diagnostics in digitizers not connected to trigger systems.

#### **Timestamp-based external discriminator**

The timestamp bit option connects the external discriminator bit to a separate multiplexer that selects one of seven different timestamp bits as the external discriminator signal. The timestamp counter generates 10ns wide pulses at rates of

- 0.745Hz (TS bit 26)

- 6.0Hz (TS bit 23)

- 23.8Hz (TS bit 21)

- 95.4Hz (TS bit 19)

- 1.5kHz (TS bit 15)

- 48.8kHz (TS bit 10)

- 195.3kHz (TS bit 8)

When the timestamp bit is selected as the external discriminator source and the channel external discriminator mode is set to "External only", the digitizer channel acts like an oscilloscope in auto-trig mode, regularly sampling the input irrespective of signal features. This is a convenient way to measure baseline levels. Alternatively, if the external discriminator mode is set to "OR" the timestamp bit may be used as a background "heartbeat" to force a discriminator hit every so often but also capture edges. This type of operation is useful for low-rate detectors (e.g. neutrino experiments) to ensure that data is regularly generated and to provide background monitoring. The higher speed timestamp bits can be used to test systemic bandwidth to exercise readout software or to test pileup response with known timing. When connected to the trigger system, timestamp-based external discriminator operation is also useful to measure variations in cable delay within the trigger cable plant that may affect triggering distinct from total delay measurements that would be done with test pulse circuits built into detector preamplifiers.

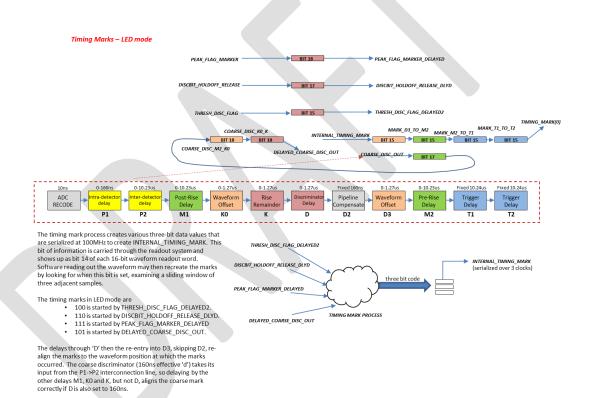

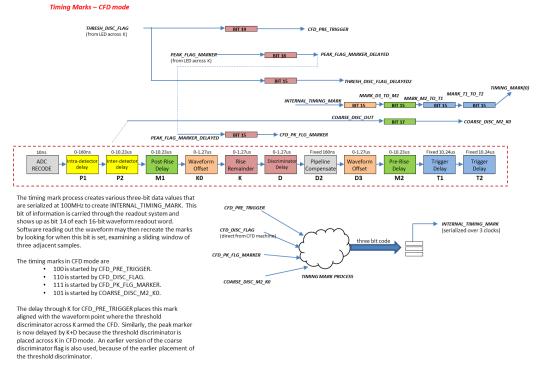

### **Insertion of timing marks into the waveform**

As the ADC chips of the digitizer module provide 14 bit data but the VME readout is 32bit words, the obvious utilization of a 32-bit word is two 16-bit halves. In each 16-bit half the ADC data value consumes bits 13:0 leaving bits 14 and 15 free for other use. Bit 14 is used to inject *timing marks* into the data so that waveform display software can show when, relative to the waveform itself, different things occur. The obvious things to highlight would be

- when the discriminator fires

- when the peak is found

- when the discriminator holdoff elapses

- when the pre-arming threshold discriminator fired to arm the constant-fraction discriminator

- when the coarse discriminator fired

- when the energy values were sampled

However, since there is only *one* bit in each 16-bit waveform value, a somewhat more creative solution must be found. The solution chosen is to *serialize* the timing mark over a fixed number of waveform data samples and to identify the feature by the n-bit serial data value. To minimize the risk of these timing marks interfering with each other, this value 'n' was set to three. Software must also be able to unambiguously identify when a timing mark starts, so the decision was made to set bit 14 to zero as default, such that the start of the timing mark is defined by bit 14 transitioning from zero to one. There are four unique three-bit codes that start with 1:

- 100

- 101

- 110

- 111

This means that there can only be four unique times marked per discriminator firing. A multiplexer is defined that changes which 3-bit code has what meaning based upon whether the discriminator is in threshold or constant-fraction mode, with a sub-selection in constant-fraction mode based upon the user's selection of whether the pre- and post-rise sums are to be sampled at the time of the arming threshold discriminator or that of the constant-fraction discriminator. This gives us the following table.

| _      |                        | in constant-fraction mode |                          |

|--------|------------------------|---------------------------|--------------------------|

| timing | in threshold mode      | energy sampled at         | energy sampled at        |

| mark   |                        | threshold discriminator   | constant fraction firing |

| code   |                        | firing                    |                          |

| 100    | discriminator fired    | CFD is armed              | CFD is armed             |

| 101    | delayed copy of coarse | delayed copy of coarse    | delayed copy of coarse   |

| 110    | holdoff time end       | when energy sampled       | when energy sampled      |

| 111    | peak found             | peak found                | peak found               |

Timing mark "101" is a *delayed* copy of the coarse discriminator, because if the mark was placed against the waveform where the coarse discriminator actually fires (~P2 + M + K + K0 + D before the threshold discriminator fires, in threshold mode), the mark would be placed so far before the rest of the waveform that most of the time it would never be seen. To compensate, the coarse discriminator bit is delayed by M (CFD mode) or M+K0+K (threshold mode) so that the timing mark for the coarse discriminator will be issued before the rising edge, but by a small enough amount to usually be in the picture. The user may subtract the known delay to estimate where the coarse discriminator actually fired.

#### Timing marks and long waveform readouts

If long waveform readouts are used, it is quite possible that multiple discriminator hits may be in one waveform. Timing marks are issued for every discriminator firing, so in this case software has to interpret multiple sets of timing marks.

#### Timing marks and down-sampling

Timing marks are generated in the 100MHz clock domain and are subject to effects from down-sampled readout. When down-sampling at any factor is in play, the 1's of the timing marks are buffered into a small FIFO that runs in parallel with the down-sampling function. This FIFO loads the timing marks in the 100MHz clock domain and unloads them at the down-sampled rate to match the waveform. This results in the timing mark data sequences with contiguous groups of 1s (100, 110, 111) being preserved for small down-sampling factors but means that at any down-sampling the "101" timing mark becomes indistinguishable from the "110" timing mark.

Additionally, with down-sampling in play, each timing mark data sequence stretches over more and more data samples as viewed in the 100MHz clock domain. As the down-sampling factor is increased, the timing marks overlap each other such that illegal timing mark sequences such as "11111111" might be seen in the down-sampled data. In general, timing marks can still be useful for down-sampling values up to 2 or maybe 3, but at any higher down-sampling factor the timing marks lose all value. Of course, if the down-sampling is set to the "on-off" mode where down-sampling is paused from the mark of the delayed coarse discriminator to the end of the down-sample holdoff time, timing marks in the full-speed "off" regions will still be rational.

#### Formation of timing marks

The logic for building the timing marks varies between threshold discriminator mode and constant-fraction discriminator mode, so two different diagrams are required.

Figure 17 - Signal delays and logic of timing marks in threshold discriminator (LED) mode.

Figure 18 - Signal delays and logic of timing marks in constant-fraction (CFD) mode.

"GammaWare", the test stand program developed at Argonne for testing all elements of the digital data acquisition systems, has been coded to process and identify timing marks in waveform data as shown in Figure 19.

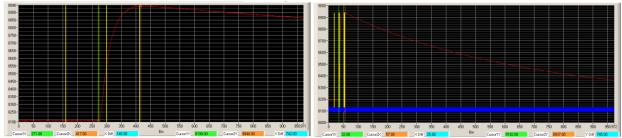

Figure 19 - Timing marks in waveforms as displayed in GammaWare.

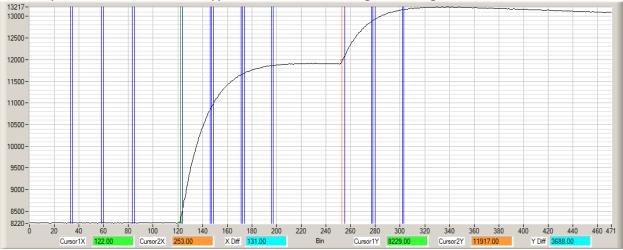

Use of the timing marks to understand waveforms and firmware operation is highly recommended. A similar GammaWare display, Figure 20, overlays rectangles whose width is proportionate to their delay time along with the timing marks. This display helps clarify the interplay between timing marks and the delay buffers. The GammaWare program displays captured waveforms the way they would look on an oscilloscope, so the order of buffers left-to-right is reversed from the firmware-centric views shown previously (e.g. Figure 5, Figure 7, etc.).

Figure 20 - GammaWare display showing both timing marks and delay buffer sizes overlaid upon waveform.

The primary observation is that the group of blocks **D3**, **D2**, **D**, **K** and **K0** are sized so that, collectively, they span the entire rise of the waveform. **D2** is a fixed delay required for

timing that is not programmable by the user. A standard practice is to set these delays such that the Post-Rise buffer starts at or immediately after the peak detector timing mark. Once that is accomplished, the **Post-Rise** and **Pre-Rise** sums clearly yield a difference proportionate to the amplitude (energy) of the signal. The P2 buffer is also shown to highlight its relationship to the Post-Rise buffer. If no pileup is occurring, as in the case of this isolated signal, the sum across the P2 buffer may be used in addition to the sum across the Post-Rise buffer to provide a greater integration time.

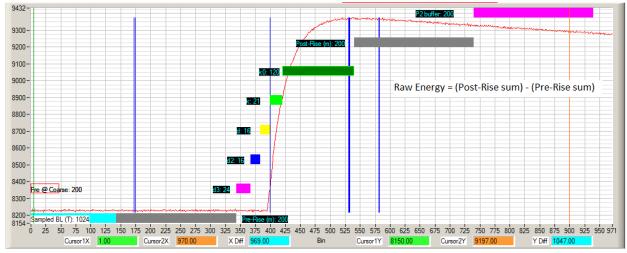

### **Energy Summation**

Obviously, the simple subtraction of **Post-Rise** – **Pre-Rise** is subject to error from polezero effects, baseline drift and offset of the pre-rise sum caused by the decay of previous pulses. Pole-zero and other corrections are better performed by software in data analysis rather than firmware. Studies at Gammasphere have shown that after appropriate pole-zero and baseline corrections derived from statistical analysis of captured waveforms are applied, waveform capture is no longer required, and the sum values saved in the header portion of the data for each event suffices to maintain resolution equivalent to traditional analog methods.

#### P2 and Energy Sums

With the release of the August 2021 firmware an accumulator function identical to that used for the Post-Rise and Pre-Rise buffers was added to the P2 buffer. This sum is reported in the data header and is logically an extension of the Post-Rise sum. As both the Post-Rise and the P2 sums are reported, analysis software may as desired use the P2 sum for a longer integration time so long as the varying number of samples in post-rise and pre-rise sums are appropriately considered. In systems where digital delay is not needed for timing alignment the firmware provides the sum across P2 for potential use in energy measurement. To further allow tuning of the firmware for the needs of any particular use case, a control bit is provided that modifies the length of the Post-Rise buffer to allow two different ways to sum up the post-rise energy.

- In SEPARATE mode, the length of the Post-Rise buffer is always identical to the length of the Pre-Rise buffer, and these are set by the "m" parameter. The length of the P2 buffer is set by the "P2" parameter.

- SEPARATE mode is the likely choice for systems that want to use P2 as a delay and/or want the simplest energy calculations.

- In SPAN mode, the length of the Pre-Rise buffer is still defined by "m", but the length of the Post-Rise buffer is modulated by the length set for P2 such that the length of the Post-Rise buffer *plus the length of the P2 buffer* is "m", and the length of the P2 buffer is set by the "P2" parameter.

- SPAN mode is the likely choice for systems that have no need to use P2 as a delay buffer and/or have high rates that may cause pileup. Here the sums across both P2 and Post-Rise may be added together for a "normal" energy sum in nonpileup situations but a lesser energy may be recoverable from using just the shorter Post-Rise in pileup or near-pileup situations.

• Pileup timing is always defined by "m" without reference to "P2".

#### Multiple Pre-Rise sums

Careful examination of Figure 20 will show an unfilled red rectangle at far left labeled "Pre @ Coarse". This shows the effect of using the coarse discriminator to capture an earlier copy of the Pre-Rise sum. Figure 21 shows approximate positions where the early pre-rise sums are collected. The data for the early pre-rise sums is always taken from the accumulator that spans the pre-rise buffer M, only the *timing* of when that sample is captured changes.

Figure 21 - approximate positions where early pre-rise sums are captured.

Operation of the pre-rise sum collection is modified by the value of the CAPTURE\_PARST\_TS bit in the channel control register. When this bit is 0, the operation is exactly as pictured in Figure 21. When the bit is 1, the second early pre-rise sample (the sample closer to the normal pre-rise sum) in the header of the event is replaced by the timestamp of the last Preamp Reset signal.

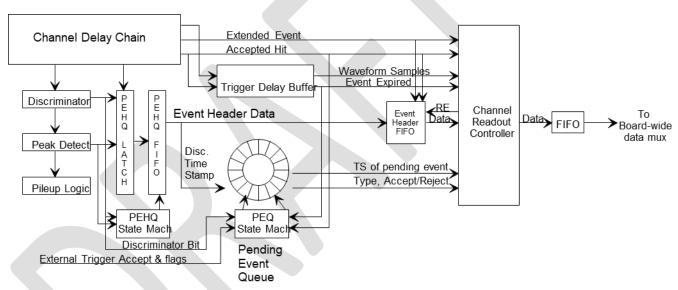

### Data Readout at the channel level

When pileup is rejected the readout of data is simple, but when pileup events are allowed through the system the readout can become quite complex. How accepted hits become accepted events has already been introduced as a concept in the section **Triggered modes vs.** "Internal Accept All" on Page 22. This section will go into greater detail regarding how the trigger selects specific events within the digitizer and will discuss issues related to readout of piled-up events. Discussion will start with operation when pileup is **rejected**, the more common usage.

#### Readout general operation when pileup is rejected

Data readout begins at the channel level where a *Channel Readout Machine* monitors the PEQ and the timestamp. As delay buffers T1 and T2 are defined as each being 1024 samples deep (thus spanning 20.48us of time at a clock of 100MHz), the sample falling out of the channel pipeline is, by definition, a fixed offset in time (based upon user settings of M, D3, D, K & K0) older than the sample currently being examined by the discriminator. By the same token a fixed numerical relationship exists between the data values in the T buffers relative to the timestamps stored within the PEQ.

In "internal accept all" mode, the readout logic operates by performing an arithmetic offset of the current timestamp based upon the delay parameters, and when the adjusted timestamp is equal to the timestamp in the PEQ, readout begins. The reader should note that since the timestamp in the PEQ is the timestamp of the discriminator, *the readout is always aligned to the discriminator firing*. The user has two control values that define the position and amount of waveform data.

- The *waveform offset* value is included in the arithmetic offset calculation that monitors the timestamp. The *waveform offset* sets how many timestamp ticks (waveform samples) *prior* to the discriminator firing the readout begins.

- The *waveform length* value defines *how many* waveform samples are read out. Because the data is packed two ADC samples per 32-bit word, the least significant bit of this value is ignored to force an even number.

#### Readout in "internal accept all" - pileup rejected

In "internal accept all" mode the PEQ is bypassed; every *accepted hit* is immediately promoted to an *accepted event* and headers are immediately transferred into the channel's *Event Header FIFO*. The readout logic simply waits for every *accepted event* to propagate far enough down the T buffers and then transfers data from the channel's pipeline into the channel's *Accepted Event FIFO* as the date range selected by the *waveform offset* and *waveform length* falls out of the pipeline. All other ADC samples not within the offset/range of the discriminator timestamps falls out of the channel pipeline and is lost. Referring to *Figure 14* - *relationship between pipeline, PEHQ, PEQ and Event Header FIFO*. on page 22 is recommended.

#### Effects of long waveform length settings; defining Readout Interference

The maximum readout length the user may select is 1024 samples and the maximum readout offset is also 1024 samples. Combinations of these two parameters can easily exceed the pileup inspection time (M+K0+K), either before or after the discriminator firing. If the waveform parameters selected by the user is longer than the pileup inspection time, event "n" may still be reading out when event "n+1" becomes ready for readout. This phenomenon is called *Readout Interference*. The readout logic is generally required to finish the readout of the current event before starting the next one, so *Readout Interference* may result in data loss and should be avoided. What will happen is that the readout length demanded will be read, and whatever portion of event "n+1" happens to fall in that length will be in the waveform data, but the *header* for event "n+1" will be lost.

Avoidance of *Readout Interference* when pileup is being rejected is simple. As the pileup inspection time is defined by (M+K0+K), ensuring that the number of waveform samples demanded for readout (the *Readout Length*), plus the number of samples prior to the edge the readout should start (the *Readout Offset*) is less than (M+K0+K+30) allows for insertion of the header and eliminates any possibility of *Readout Interference*.

#### **Down-sampled readout**

The user may select down-sampling factors from 0 to 7, meaning that the waveform data will be presented as samples that average together  $2^N$  samples per waveform point (1 to 128 ADC samples per data point for  $0 \le N \le 7$ ). The down-sampling logic acts by using a running accumulator that spans  $2^N$  samples, adjusted every 10ns, but only read out once every  $2^N$  samples. The sum is then shifted right N bits (integer division) and this is the datum provided each down-sampled waveform sample.

The waveform sample data read out by the digitizer consists of two 16-bit halves per 32bit word, but the ADC data is only 14 bits wide. One of the two extra bits in each 16-bit half identifies transitions between down-sampled and normal speed waveform samples. Downsampling may be applied to the waveform readout the same for all values or may be set to operate in an "on-off" mode. In the "on-off" mode, data starts out down-sampled, but the logic looks for the *Timing Mark* indicative of the coarse discriminator firing and pauses downsampling when this is seen. The pause in down-sampling lasts for the number of words defined by a control register, after which down-sampling starts up again.

#### **Readout Interference and down-sampling**

When down-sampling is in effect the *time* required to read out a down-sampled waveform increases with the down-sampling factor. This is because the internal processing of down-sampling and packing words into the output data still must use every full-speed data value at the same 100MHz processing rate that is contained in the time span of the down-sampled readout. The system itself does not change speed. Because of this, the risk of *Readout Interference* when down-sampling is enabled is much greater.

#### Readout of piled-up events

If pileup rejection is turned off, the readout logic must now process all *Extended Events* in addition to *Accepted Hits*. An obvious consequence of this is that the time between discriminator firings will often be quite short, limited now only by the discriminator hold-off time. With typical register settings this means that edges could occur separated by ~1us rather than many microseconds.

Control of how the firmware handles this readout is implemented in two levels. The first level of control is named *Pileup Extension Enable*.

- When Pileup Extension is *disabled* the readout logic is constrained to process only

Accepted Hits that have become Accepted Events. This means that isolated events (no

pileup) and the first event of a pileup train may potentially be read out, but that the 2<sup>nd</sup>